¿Qué es un convertidor ADC (convertidor analógico a digital)?

April 13, 2026

En este artículo revisaremos qué es un convertidor A/D (ADC) y cuáles son los principales tipos en uso hoy en día, describiendo cada uno con suficiente detalle para que usted:

Ver la tecnología básica de cada tipo de ADC

Aprender sobre las características y capacidades clave de los ADC

Entender qué tipos de ADC funcionan mejor para las aplicaciones actuales

Descubrir qué dos tipos principales de ADC ha seleccionado Dewesoft, y por qué

¿Está listo para empezar? ¡Empecemos!

¿Qué es un ADC (convertidor analógico-digital)?

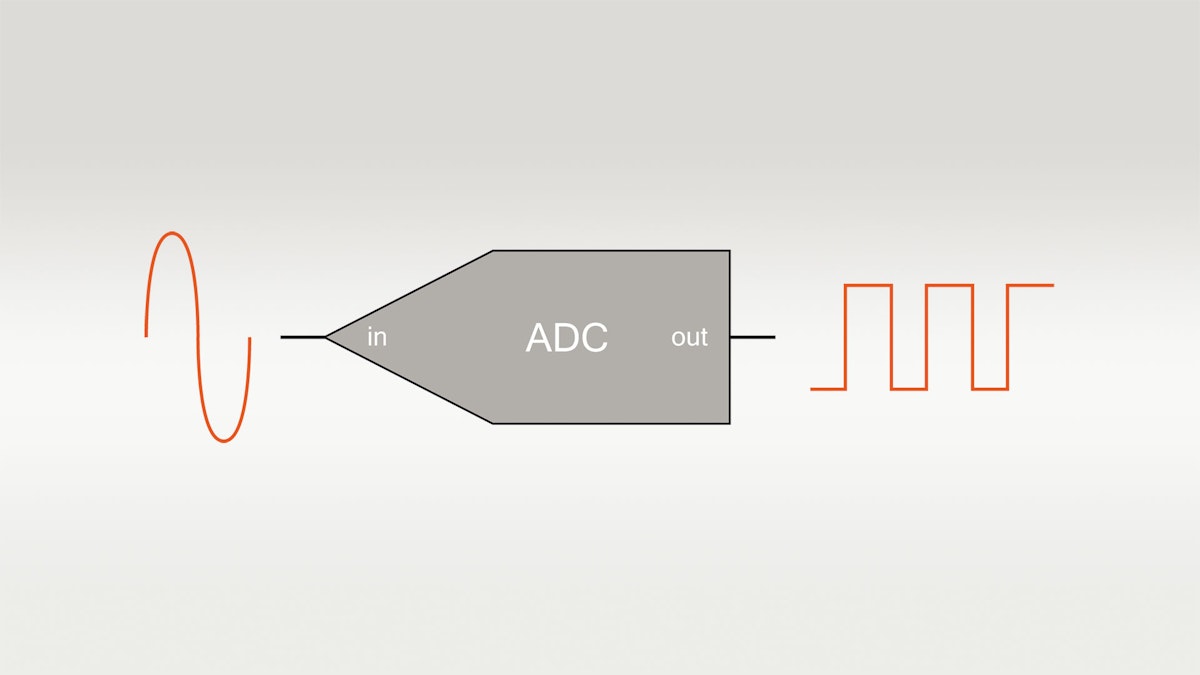

El convertidor analógico-digital (ADC) es uno de los bloques fundamentales de los sistemas modernos de adquisición de datos (también conocidos como sistemas DAQ o DAS). Estos sistemas están compuestos por los siguientes componentes básicos:

Sensores

Acondicionamiento de señal

Convertidor analógico-digital (ADC) (este artículo)

Y algún tipo de computadora con software DAQ para el registro y análisis de señales.

Los convertidores ADC desempeñan un papel importante en los sistemas modernos de adquisición de datos digitales.

Aprende más sobre adquisición de datos:

¿Qué hacen los convertidores ADC?

El propósito principal de los convertidores A/D dentro de un sistema de adquisición de datos es convertir señales analógicas acondicionadas en un flujo de datos digitales para que el sistema de adquisición de datos pueda procesarlos para su visualización, almacenamiento y análisis.

Leer también:

Tipos principales de convertidores ADC

Aunque hoy en día existen cinco tipos principales de ADC, en el mundo moderno de DAQ en realidad se reduce a dos de ellos:

aproximación sucesiva y

delta-sigma.

Los otros tipos son perfectamente válidos, pero están mejor adaptados a aplicaciones fuera del ámbito DAQ. Por ejemplo, los ADC de doble pendiente son bastante lentos y, por lo tanto, se encuentran principalmente en voltímetros portátiles.

También existen los ADC Flash que ofrecen frecuencias de muestreo extremadamente altas, pero con una resolución en el eje de amplitud demasiado baja para aplicaciones DAQ. Los ADC tipo Pipeline utilizan múltiples convertidores flash para mejorar la resolución en el eje de amplitud, pero aún así están limitados en ese aspecto.

Comparación de los principales tipos de ADC

| Tipo de ADC | Ventajas | Desventajas | Resolución máxima | Frecuencia de muestreo máxima |

|---|---|---|---|---|

| Doble pendiente | Económico | Baja velocidad | 20 bits | 100 Hz |

| Flash | Muy rápido | Baja resolución en bits | 12 bits | 10 GHz |

| Pipeline | Muy rápido | Resolución limitada | 16 bits | 1 GHz |

| SAR | Buena relación velocidad/resolución | Sin protección anti-aliasing inherente | 18 bits | 10 MHz |

| Delta-sigma (ΔΣ) | Alto rendimiento dinámico, protección anti-aliasing inherente | Histéresis en señales no naturales | 32 bits | 1 MHz |

Así que, nuevamente, el mundo DAQ se ha centrado en los ADC SAR (aproximación sucesiva) y los ADC delta-sigma (ΔΣ). Cada uno tiene sus propias ventajas y desventajas y, por lo tanto, su idoneidad para ciertas aplicaciones. A continuación, veremos cómo funciona cada ADC y los compararemos.

Aprende más:

ADC de aproximación sucesiva (SAR)

El ADC “pan de cada día” en el mundo DAQ es el convertidor analógico-digital SAR. Ofrece un excelente equilibrio entre velocidad y resolución y maneja una amplia variedad de señales con gran fidelidad.

Existe desde hace mucho tiempo, por lo que los diseños SAR son estables y confiables, y los chips son relativamente económicos. Pueden configurarse tanto para tarjetas A/D de gama baja, donde un solo chip ADC se “comparte” entre múltiples canales de entrada (tarjetas A/D multiplexadas), como en configuraciones donde cada canal de entrada tiene su propio ADC para un muestreo verdaderamente simultáneo.

La entrada analógica de la mayoría de los ADC es de 5 V, por lo que casi todos los front-ends de acondicionamiento de señal proporcionan una salida acondicionada igual. El ADC SAR típico utiliza un circuito de muestreo y retención que toma el voltaje analógico acondicionado del front-end de acondicionamiento de señal.

Un DAC integrado crea un voltaje analógico de referencia igual al código digital de salida del circuito de muestreo y retención. Ambos se envían a un comparador que transmite el resultado de la comparación al SAR. Este proceso continúa “n” veces sucesivas, siendo “n” la resolución en bits del propio ADC, hasta que se encuentra el valor más cercano a la señal real.

Los ADC SAR no tienen filtrado anti-aliasing (AAF) inherente, por lo que, a menos que esto se agregue antes del ADC por el sistema DAQ, si el ingeniero selecciona una frecuencia de muestreo demasiado baja, señales falsas (también llamadas “alias”) serán digitalizadas por el ADC SAR. El aliasing es particularmente problemático porque es imposible corregirlo después de la digitalización.

No hay forma de solucionarlo con software. Debe prevenirse ya sea muestreando siempre por encima de la frecuencia de Nyquist de todas las señales de entrada o filtrando las señales antes y dentro del ADC.

Para más detalles, ver Aliasing y el peligro del submuestreo más abajo

Los ADC SAR son una opción sólida para muchos sistemas DAQ en uso hoy en día. Se utilizan ampliamente en el extremo inferior del mercado, ya que pueden emplearse de forma multiplexada, donde múltiples canales se muestrean con un solo ADC. Pero también se utilizan ampliamente en el segmento medio del mercado debido a su velocidad y buena resolución en el eje de amplitud.

Debido a su limitada resolución en el eje de amplitud, no son adecuados para aplicaciones altamente dinámicas como ruido, audio, choque y vibración, equilibrado, procesamiento de señales sinusoidales, etc. Para estas aplicaciones, los ingenieros deben recurrir a los ADC delta-sigma, como se describe en la siguiente sección.

ADC Sigma-delta (ΔΣ)

Un diseño más reciente de ADC es el ADC delta-sigma, que aprovecha la tecnología DSP para mejorar la resolución en el eje de amplitud y reducir el ruido de cuantización de alta frecuencia inherente a los diseños SAR.

El diseño complejo y potente de los ADC delta-sigma los hace ideales para aplicaciones dinámicas que requieren la mayor resolución posible en el eje de amplitud. Por eso se encuentran comúnmente en audio, sonido, vibración y en una amplia gama de aplicaciones de adquisición de datos de alta gama.

La implementación de estos chips para aplicaciones de adquisición de datos suele implicar una gran atención al filtrado anti-aliasing (AAF) en el front-end, haciendo prácticamente imposible digitalizar señales falsas.

Un filtro pasa-bajo implementado en un DSP elimina prácticamente el ruido de cuantización, lo que da como resultado un excelente rendimiento de relación señal-ruido.

Los ADC delta-sigma funcionan sobremuestreando las señales muy por encima de la frecuencia de muestreo seleccionada. El DSP luego crea un flujo de datos de alta resolución a partir de estos datos sobremuestreados a la velocidad que el usuario ha seleccionado. Este sobremuestreo puede ser hasta cientos de veces mayor que la frecuencia de muestreo seleccionada. Este enfoque crea un flujo de datos de muy alta resolución (24 bits es común) y tiene la ventaja de permitir un filtrado anti-aliasing (AAF) de múltiples etapas, haciendo prácticamente imposible digitalizar señales falsas.

ADC dual sigma-delta - DualCoreADC®

Dewesoft ha aprovechado aún más estos ADC combinando dos de ellos en cada canal de entrada. Un ADC se configura con baja ganancia y el otro con una ganancia más alta. Ambos ADC monitorean la señal al mismo tiempo, y un circuito propietario los compara en tiempo real y utiliza el que tiene la mejor relación señal-ruido en cada momento, fusionando las señales digitales paralelas en un único flujo continuo con un rango dinámico significativamente mejorado.

Esta técnica mejora enormemente el rango dinámico, que de otro modo sería imposible de alcanzar con un solo ADC. Aumenta el rango dinámico hasta 160 dB. Dewesoft ha patentado esta tecnología, que se denomina DualCoreADC en el mercado.

Es interesante señalar que incluso con señales muy lentas, como las de la mayoría de los termopares, la mayor resolución posible en el eje de amplitud hace que estos ADC delta-sigma sean preferibles a los ADC SAR.

Imagina un termopar capaz de medir en un rango de 1500°, cuanto mayor sea la resolución en el eje de amplitud en el ADC, mayor será la resolución de la señal de temperatura. Ten en cuenta que cada bit duplica efectivamente la resolución en el eje vertical.

¿Qué ADC es mejor? ¿SAR o sigma-delta?

Cada tecnología ADC tiene su lugar. Y dado que las aplicaciones son tan diferentes, es imposible decir que una es mejor que otra en general. Sin embargo, sí es absolutamente posible decir que una es mejor que otra con respecto a uno o más de los requisitos de las aplicaciones actuales:

| Criterio | SAR ADCs | Sigma-Delta (ΔΣ) ADCs |

|---|---|---|

| Cuando se necesita la mejor resolución en el eje de amplitud (incluso para señales lentas como termopares). | Normalmente 16 o 18 bits como máximo. | Mejor opción. 24 bits es el estándar de facto entre las tarjetas ΔΣ hoy en día. |

| Cuando se debe utilizar una tarjeta A/D multiplexada económica. | Única opción. Es posible multiplexar un solo ADC SAR para múltiples canales y crear sistemas DAQ económicos cuando los pequeños errores de desfase temporal no son un problema. | N/A |

| Cuando se requiere la mayor frecuencia de muestreo posible. | Mejor opción. Existen ADC SAR para adquisición de datos con hasta 10 MS/s de muestreo. | El procesamiento DSP integrado limita la frecuencia de muestreo máxima de los ADC ΔΣ en comparación con los ADC SAR. |

| Cuando se desea AAF (filtrado anti-aliasing). | Costoso y complejo de añadir a los ADC SAR. | Mejor opción, ya que el AAF es inherente a los ADC ΔΣ. |

| Cuando se necesita la mayor relación señal-ruido. | La única opción. Es posible alcanzar hasta 160 dB con la tecnología propietaria DualCoreADC® de Dewesoft. | |

| Cuando se registrarán principalmente señales no naturales (como ondas cuadradas). | Cuando se registrarán principalmente señales no naturales (como ondas cuadradas). |

Lee más sobre los diferentes tipos de convertidores ADC:

La herramienta adecuada para el trabajo

Aunque Dewesoft es conocido por utilizar ADC sigma-delta de 24 bits y ha innovado significativamente con la tecnología DualCoreADC, también utiliza ADC SAR de 16 bits para lograr mayores frecuencias de muestreo (hasta 15 MS/s).

Estos son los acondicionadores de señal SIRIUS HS (alta velocidad) y SIRIUS XHS (velocidad extra alta) disponibles dentro de esa línea.

Estos acondicionadores de señal implementan un potente filtrado AAF en forma de filtros anti-aliasing de 5.º orden a 100 kHz. Existe un filtro adicional en el dominio digital seleccionable entre Bessel, Butterworth (o bypass), hasta el 8.º orden.

El filtrado anti-aliasing potente está integrado en todos los acondicionadores de señal con ADC de 24 bits de Dewesoft.

¿Multiplexado o un ADC por canal?

Muy a menudo en sistemas DAQ de gama baja, como registradores de datos o sistemas de control industrial, se utilizan tarjetas A/D multiplexadas, porque son menos costosas que las tarjetas A/D que tienen un ADC separado por cada canal de entrada.

En un sistema ADC multiplexado, un solo convertidor analógico-digital se utiliza para convertir múltiples señales del dominio analógico al digital. Esto se hace multiplexando las señales analógicas una por una hacia el ADC.

Este es un enfoque de menor costo, pero no es posible alinear con precisión las señales en el eje de tiempo, porque solo una señal puede convertirse en un momento dado. Por lo tanto, siempre existe un desfase temporal entre canales. Si un pequeño error de desfase temporal es irrelevante en una aplicación determinada, entonces no necesariamente es algo negativo. Lo mismo ocurre con los dispositivos analógicos utilizados dentro del sistema, elegir la mejor opción para la aplicación en términos de forma, ajuste, función y evitar la obsolescencia son factores determinantes.

Además, dado que la frecuencia de muestreo máxima siempre se divide por el número de canales que se están muestreando, la frecuencia máxima por canal suele ser menor en sistemas multiplexados, excepto en los casos en los que solo se muestrea uno o unos pocos canales.

En los sistemas modernos de adquisición de datos, los sistemas ADC multiplexados se utilizan principalmente en sistemas DAQ de gama baja, donde el costo es más importante que la precisión o la velocidad.

¿Qué es la frecuencia de muestreo?

La velocidad a la que se convierten las señales se llama la frecuencia de muestreo. Ciertas aplicaciones, como la mayoría de las mediciones de temperatura, no requieren una frecuencia alta, ya que las señales no cambian muy rápidamente.

Sin embargo, los voltajes y corrientes AC, el choque y la vibración, y muchas otras aplicaciones requieren frecuencias de muestreo en el rango de decenas o cientos de miles de muestras por segundo o más. La frecuencia de muestreo suele referirse como el eje T (o X) de la medición.

Dewesoft ofrece sistemas DAQ con frecuencias de muestreo máximas, como se muestra aquí:

| Modelo | Variante | Interfaz | Frecuencia de muestreo máx. (por canal) |

|---|---|---|---|

| SIRIUS | Doble núcleo | USB 2.0 | 200 kS/s |

| SIRIUS MINI | Doble núcleo | USB 2.0 | 200 kS/s |

| SIRIUS | Doble núcleo | EtherCAT | 20 kS/s |

| SIRIUS | HD (alta densidad) | USB 2.0 | 200 kS/s |

| SIRIUS | HD (alta densidad) | EtherCAT | 20 kS/s |

| SIRIUS | HS (alta velocidad) | USB 2.0 | 1 MS/s |

| SIRIUS | XHS (velocidad extra alta) | USB 3 / Gigabit LAN | 15 MS/s |

| DEWE-43A | / | USB 2.0 | 200 kS/s |

| MINITAURs | / | USB 2.0 | 200 kS/s |

| KRYPTON | Multicanal | EtherCAT | 20 kS/s |

| KRYPTON | Un canal | EtherCAT | 40 kS/s |

| IOLITE | Rack | EtherCAT | 20 kS/s |

| IOLITE | Modular | EtherCAT | 20 kS/s |

Aliasing y el peligro del submuestreo

Comprender tus señales y sus frecuencias máximas posibles es una parte importante para obtener mediciones precisas. Por ejemplo, supongamos que queremos medir la salida de un acelerómetro.

Si esperamos que experimente vibraciones con una frecuencia máxima de 100 Hz, debemos establecer la frecuencia de muestreo al menos al doble de ese valor (la frecuencia de Nyquist), pero en la práctica es mejor un sobremuestreo de diez veces para obtener una representación de buena calidad de la forma de la señal. Así que en este ejemplo, establecemos la frecuencia de muestreo en 1000 Hz y realizamos la medición.

Teóricamente, todo debería estar bien, pero ¿cómo sabemos que la señal no alcanzó realmente una frecuencia mucho más alta con una amplitud considerable? Si lo hizo, entonces nuestro sistema no mediría ni convertiría la señal con precisión. Y, de hecho, si esto se lleva al extremo, los valores medidos podrían incluso ser completamente incorrectos.

Para entender el aliasing, observa una película antigua donde una cámara filmaba a 24 fotogramas por segundo mientras pasaba un carro; a ciertas velocidades puede parecer que las ruedas giran hacia atrás, o incluso que no se mueven en absoluto.

Este es un tipo de efecto visual estroboscópico causado por la relación armónica entre la frecuencia de rotación de la rueda y la velocidad de captura de imágenes de la cámara. Quizás hayas visto videos donde la velocidad de obturación de una cámara estaba sincronizada con las aspas de un helicóptero, haciendo que parezca que el helicóptero está suspendido en el aire, con las aspas sin moverse en absoluto.

En el caso de una película o un video entretenido no importa, pero al realizar una medición científica, si realmente creemos que las ruedas de un automóvil giran hacia atrás, o que las aspas de un helicóptero no se mueven, cuando en realidad lo hacen muy rápido, tenemos un problema real de medición.

En términos de digitalizar señales de voltaje con nuestro ADC, es importante que la frecuencia de muestreo se establezca adecuadamente. Si la configuramos demasiado alta, desperdiciamos potencia de procesamiento y terminamos con archivos de datos innecesariamente grandes y difíciles de manejar. Pero si la configuramos demasiado baja, podríamos tener dos problemas:

Perder componentes dinámicos vitales de la señal

Terminar con señales falsas (“alias”) (si el sistema carece de filtrado anti-aliasing)

Prevención del aliasing

Los productos Dewesoft previenen el aliasing utilizando ADC de 24 bits que tienen filtros anti-aliasing (AAF) integrados. Estos filtros funcionan en varias etapas, incluyendo una etapa que se ajusta automáticamente a la frecuencia de Nyquist (generalmente alrededor del 40%) de la frecuencia de muestreo seleccionada. Por lo tanto, incluso si seleccionas una frecuencia de muestreo demasiado baja, las señales falsas o “alias” no pueden arruinar la medición.

¿Qué es la resolución en bits y por qué es importante?

En los primeros días de la adquisición de datos, los ADC de 8 bits eran comunes. En la actualidad, en el mundo de los sistemas DAQ, los ADC de 24 bits son estándar en la mayoría de los sistemas de adquisición de datos diseñados para realizar mediciones dinámicas, y los ADC de 16 bits se consideran comúnmente la resolución mínima para señales en general. Existen algunos sistemas de gama baja que utilizan ADC de 12 bits.

Dado que cada bit de resolución duplica efectivamente la resolución posible, los sistemas con ADC de 24 bits proporcionan 2^24 = 16,777,216. Por lo tanto, una señal entrante de un voltio puede dividirse en más de 16 millones de pasos en el eje Y.

16,777,216 pasos para un ADC de 24 bits es significativamente mejor que los 65,656 pasos teóricos máximos de un ADC de 16 bits. Por lo tanto, la representación de las formas de onda es mucho más precisa y detallada cuanto mayor es la resolución. Esto también se aplica al eje de tiempo.

Tecnología DualCoreADC® y por qué es importante

En el eje de amplitud, uno de los desafíos que los ingenieros han enfrentado durante años es el rango dinámico. Por ejemplo: ¿qué sucede si tenemos una señal que normalmente es inferior a 5 voltios, pero que en ocasiones puede aumentar drásticamente? Si configuramos la resolución del ADC para adaptarse a los datos de 0-5 V, el sistema se saturará completamente cuando la señal supere ese valor.

Una solución sería utilizar dos canales configurados con diferentes ganancias y referirse a uno de ellos para los datos de 0-5 V, y al otro para los datos de mayor amplitud. Pero esto es muy ineficiente, no podemos usar dos canales para cada señal de entrada, necesitaríamos el doble de sistemas DAQ para realizar el mismo trabajo. Además, haría que el análisis de datos después de cada prueba fuera mucho más complejo y llevara más tiempo.

La tecnología DualCoreADC® de Dewesoft resuelve este problema utilizando dos ADC de 24 bits independientes por canal, cambiando automáticamente entre ellos en tiempo real y creando un único canal continuo. Estos dos ADC siempre miden la ganancia alta y baja de la señal de entrada. Esto da como resultado el rango de medición completo posible del sensor y evita que la señal se recorte.

Descubre los sistemas de adquisición de datos de Dewesoft en la página de productos, con acondicionamiento de señal de alta gama

Con la tecnología DualCoreADC®, los sistemas DAQ SIRIUS alcanzan más de 130 dB de relación señal-ruido y más de 160 dB de rango dinámico. Esto es 20 veces mejor que los sistemas típicos de 24 bits, con 20 veces menos ruido.

Resumen

La elección de qué tecnología ADC emplear debe basarse siempre en los requisitos de la aplicación. Si estás midiendo principalmente señales estáticas y cuasi estáticas (lentas), obviamente no necesitas un sistema de muy alta velocidad, pero probablemente quieras uno con la mayor resolución posible en el eje de amplitud.

Los sistemas fijos utilizados en la industria suelen tener requisitos que no cambian mucho, y normalmente es más fácil elegir un sistema.

Sin embargo, para sistemas DAQ de uso general, es un poco más desafiante, ya que estos sistemas se utilizan en una variedad de aplicaciones a lo largo del tiempo. La clave es seleccionar uno que tenga el mejor rendimiento global y protección contra el ruido, el aliasing y la obsolescencia.